MICROCHIP PIC24 Flash програмиране

Информация за продукта

Flash програмиране

Семействата устройства dsPIC33/PIC24 имат вътрешна програмируема флаш програмна памет за изпълнение на потребителски код. Има до три метода за програмиране на тази памет:

- Таблица Инструкция Операция

- Вътрешно-схемно серийно програмиране (ICSP)

- Програмиране в приложението (IAP)

Инструкциите в таблицата предоставят метода за прехвърляне на данни между пространството на паметта на Flash програмата и пространството на паметта за данни на устройства dsPIC33/PIC24. Инструкцията TBLRDL се използва за четене от битове [15:0] на програмното пространство в паметта. Инструкцията TBLWTL се използва за запис в битове [15:0] от пространството в паметта на Flash програмата. TBLRDL и TBLWTL имат достъп до паметта на Flash програмата в режим Word или Byte.

В допълнение към адреса на паметта на Flash програмата, инструкцията на таблицата също така определя W регистър (или W регистър указател към място в паметта), който е източникът на данните от паметта на Flash програмата, които трябва да бъдат записани, или дестинацията за Flash програма четене на паметта.

Този раздел описва техниката за програмиране на Flash програмна памет. Семействата устройства dsPIC33/PIC24 имат вътрешна програмируема флаш програмна памет за изпълнение на потребителски код. Има до три метода за програмиране на тази памет:

- Самопрограмиране по време на изпълнение (RTSP)

- In-Circuit Serial Programming™ (ICSP™)

- Подобрено серийно програмиране в веригата (EICSP)

RTSP се изпълнява от приложния софтуер по време на изпълнение, докато ICSP и EICSP се изпълняват от външен програмист, използващ серийна връзка за данни към устройството. ICSP и EICSP позволяват много по-бързо време за програмиране от RTSP. RTSP техниките са описани в раздел 4.0 „Самопрограмиране по време на изпълнение (RTSP)“. Протоколите ICSP и EICSP са дефинирани в документите за програмни спецификации за съответните устройства, които могат да бъдат изтеглени от Microchip webсайт (http://www.microchip.com). При програмиране на езика C са налични няколко вградени функции, които улесняват Flash програмирането. Вижте „Ръководство на потребителя на MPLAB® XC16 C компилатор“ (DS50002071) за подробности относно вградените функции.

Инструкции за употреба на продукта

За да програмирате Flash програмната памет, изпълнете следните стъпки:

- Обърнете се към листа с данни на устройството, за да проверите дали разделът на ръководството за семейни справки поддържа устройството, което използвате.

- Изтеглете листа с данни на устройството и секциите на справочното ръководство за семейството от Microchip Worldwide Webсайт на: http://www.microchip.com.

- Изберете един от трите метода за програмиране на паметта (операция с таблични инструкции, серийно програмиране в схемата (ICSP), програмиране в приложението (IAP)).

- Ако използвате операция с таблична инструкция, използвайте инструкцията TBLRDL за четене от битове [15:0] от пространството на паметта на програмата и инструкцията TBLWTL за запис в битове [15:0] от пространството в паметта на Flash програмата.

- Уверете се, че сте посочили W регистър (или W регистър указател към място в паметта) като източник на данни от паметта на Flash програма, които трябва да бъдат записани, или дестинация за четене на памет на Flash програма.

За допълнителна информация и подробности относно програмирането на флаш програмната памет вижте Справочното ръководство за семейството dsPIC33/PIC24.

ТАБЛИЦА ИНСТРУКЦИЯ ОПЕРАЦИЯ

Инструкциите в таблицата предоставят метода за прехвърляне на данни между пространството на паметта на Flash програмата и пространството на паметта за данни на устройства dsPIC33/PIC24. Този раздел предоставя обобщение на табличните инструкции, използвани по време на програмирането на флаш програмната памет. Има четири основни инструкции за таблицата:

- TBLRDL: Ниско четене на таблицата

- TBLRDH: Таблица Прочетете високо

- TBLWTL: Table Write Low

- TBLWTH: Table Write High

Инструкцията TBLRDL се използва за четене от битове [15:0] на програмното пространство в паметта. Инструкцията TBLWTL се използва за запис в битове [15:0] от пространството в паметта на Flash програмата. TBLRDL и TBLWTL имат достъп до паметта на Flash програмата в режим Word или Byte.

Инструкциите TBLRDH и TBLWTH се използват за четене или запис на битове [23:16] от пространството на програмната памет. TBLRDH и TBLWTH имат достъп до паметта на Flash програмата в режим Word или Byte. Тъй като Flash програмната памет е широка само 24 бита, инструкциите TBLRDH и TBLWTH могат да адресират горен байт от Flash програмната памет, който не съществува. Този байт се нарича "фантомен байт". Всяко четене на фантомния байт ще върне 0x00. Записването във фантомния байт няма ефект. 24-битовата Flash програмна памет може да се разглежда като две разположени едно до друго 16-битови пространства, като всяко пространство споделя един и същ адресен диапазон. Следователно инструкциите TBLRDL и TBLWTL имат достъп до „ниското“ пространство на програмната памет (PM[15:0]). Инструкциите TBLRDH и TBLWTH осъществяват достъп до „високото“ програмно пространство (PM[31:16]). Всяко четене или запис в PM[31:24] ще има достъп до фантомния (неимплементиран) байт. Когато някоя от инструкциите на таблицата се използва в байтов режим, най-малкият бит (LSb) на адреса на таблицата ще се използва като бит за избор на байт. LSb определя кой байт във високото или ниското пространство на програмната памет е достъпен.

Фигура 2-1 илюстрира как паметта на Flash програмата се адресира с помощта на инструкциите в таблицата. 24-битов програмен адрес на паметта се формира с помощта на битове [7:0] от регистъра TBLPAG и ефективния адрес (EA) от W регистър, указан в инструкцията на таблицата. 24-битовият програмен брояч (PC) е илюстриран на фигура 2-1 за справка. Горните 23 бита на EA се използват за избор на място в паметта на Flash програмата.

За инструкциите на таблицата на байтовия режим, LSb на W регистър EA се използва за избор кой байт от 16-битовата дума на паметта на Flash програмата да бъде адресирана; '1' избира битове [15:8] и '0' избира битове [7:0]. LSb на W регистър EA се игнорира за таблична инструкция в режим Word. В допълнение към адреса на паметта на Flash програмата, инструкцията на таблицата също така определя W регистър (или W регистър указател към място в паметта), който е източникът на данните от паметта на Flash програмата, които трябва да бъдат записани, или дестинацията за Flash програма четене на паметта. За операция за запис на таблица в байтов режим, битове [15:8] от работния регистър източник се игнорират.

Използване на инструкции за четене на таблица

Четенето на таблица изисква две стъпки:

- Адресният указател се настройва с помощта на регистъра TBLPAG и един от W регистрите.

- Съдържанието на паметта на Flash програмата в местоположението на адреса може да бъде прочетено.

- РЕЖИМ ЗА ЧЕТЕНЕ НА ДУМА

Кодът, показан в Example 2-1 и Example 2-2 показва как да четете дума от паметта на Flash програма, като използвате инструкциите в таблицата в режим Word.

- РЕЖИМ ЗА ЧЕТЕНЕ НА БАЙТОВЕ

Кодът, показан в ExampLe 2-3 показва оператора след нарастване при четене на ниския байт, което кара адреса в работния регистър да се увеличава с единица. Това задава EA[0] на '1' за достъп до средния байт в третата инструкция за запис. Последното пост-инкремент задава W0 обратно към четен адрес, сочейки към следващото място в паметта на Flash програмата.

- РЕЗЕТА ЗА ПИСАНЕ НА ТАБЛИЦА

Инструкциите за запис на таблица не записват директно в енергонезависимата програмна памет. Вместо това инструкциите за запис на таблица зареждат ключалки за запис, които съхраняват данните за запис. Адресните регистри на NVM трябва да бъдат заредени с първия адрес, където трябва да се записват фиксираните данни. Когато всички ключалки за запис са заредени, действителната операция по програмиране на паметта се стартира чрез изпълнение на специална последователност от инструкции. По време на програмирането хардуерът прехвърля данните в ключалките за запис към флаш памет. Резетата за запис винаги започват от адрес 0xFA0000 и се простират до 0xFA0002 за програмиране на думи или през 0xFA00FE за устройства, които имат програмиране на редове.

Забележка: Броят на ключалките за запис варира според устройството. Обърнете се към главата „Flash Program Memory“ на конкретния лист с данни за устройството за броя на наличните ключалки за запис.

КОНТРОЛНИ РЕГИСТРИ

Няколко специални функционални регистъра (SFR) се използват за програмиране на операциите за изтриване и запис на флаш програмната памет: NVMCON, NVMKEY и NVM адресните регистри, NVMADR и NVMADRU.

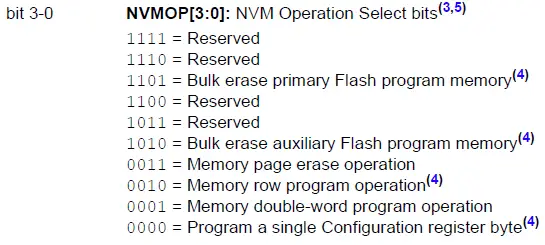

NVMCON регистър

Регистърът NVMCON е основният контролен регистър за Flash и операции по програмиране/изтриване. Този регистър избира дали ще бъде извършена операция по изтриване или програмиране и може да стартира програмата или цикъла на изтриване. Регистърът NVMCON е показан в регистър 3-1. Долният байт на NVMCON конфигурира типа NVM операция, която ще бъде изпълнена.

NVMKEY Регистрирайте се

Регистърът NVMKEY (вижте регистър 3-4) е регистър само за запис, използван за предотвратяване на случайни записи на NVMCON, които могат да повредят флаш паметта. Веднъж отключени, записите в NVMCON са разрешени за един цикъл на инструкция, в който WR битът може да бъде настроен да извиква изтриване или рутинна програма. Като се имат предвид изискванията за синхронизиране, се изисква деактивиране на прекъсванията.

Изпълнете следните стъпки, за да започнете последователност от изтриване или програмиране:

- Деактивирайте прекъсванията.

- Напишете 0x55 на NVMKEY.

- Напишете 0xAA на NVMKEY.

- Стартирайте цикъла на запис на програмиране, като зададете бита WR (NVMCON[15]).

- Изпълнете две NOP инструкции.

- Възстановяване на прекъсванията.

ИЗКЛЮЧВАНЕ НА ПРЕКЪСВАНИЯТА

Деактивирането на прекъсванията е необходимо за всички Flash операции, за да се гарантира успешен резултат. Ако възникне прекъсване по време на последователността за отключване на NVMKEY, то може да блокира записа в бита WR. Последователността за отключване на NVMKEY трябва да се изпълнява без прекъсване, както е обсъдено в раздел 3.2 „Регистър на NVMKEY“.

Прекъсванията могат да бъдат деактивирани по един от двата метода, чрез деактивиране на Global Interrupt Enable (GIE бит) или чрез използване на инструкцията DISI. Инструкцията DISI не се препоръчва, тъй като забранява само прекъсвания с приоритет 6 или по-нисък; следователно трябва да се използва методът за разрешаване на глобално прекъсване.

CPU записва в GIE отнема два цикъла на инструкции, преди да повлияе на кодовия поток. След това са необходими две NOP инструкции или могат да бъдат заменени с други полезни работни инструкции, като например зареждане на NVMKEY; това е приложимо както за установени, така и за изчистени операции. Трябва да се внимава при повторно активиране на прекъсвания, така че насочената NVM рутина да не позволява прекъсвания, когато предишна извикана функция ги е деактивирала по други причини. За да се реши това в Асемблирането, може да се използва натискане и изскачане на стека, за да се запази състоянието на GIE бита. В C променлива в RAM може да се използва за съхраняване на INTCON2 преди изчистване на GIE. Използвайте следната последователност, за да деактивирате прекъсванията:

- Натиснете INTCON2 върху стека.

- Изчистете GIE бита.

- Два NOP или запис в NVMKEY.

- Стартирайте цикъла на програмиране, като зададете бита WR (NVMCON[15]).

- Възстановете състоянието на GIE чрез POP на INTCON2.

NVM адресни регистри

Двата NVM адресни регистъра, NVMADRU и NVMADR, когато са свързани, формират 24-битовия EA на избрания ред или дума за програмни операции. Регистърът NVMADRU се използва за съхранение на горните осем бита на EA, а регистърът NVMADR се използва за задържане на долните 16 бита на EA. Някои устройства може да се отнасят към същите тези регистри като NVMADRL и NVMADRH. Адресните регистри на NVM трябва винаги да сочат към двойна граница на думата с инструкции, когато се извършва операция по програмиране на дума с двойна инструкция, граница на ред, когато се извършва операция по програмиране на ред, или граница на страница, когато се извършва операция за изтриване на страница.

Регистър 3-1: NVMCON: Контролен регистър на флаш паметта

Забележка

- Този бит може да бъде нулиран (т.е. изчистен) само при нулиране при включване (POR).

- При излизане от режим на неактивност има забавяне при включване (TVREG), преди Flash програмната памет да започне да работи. Обърнете се към главата „Електрически характеристики“ на спецификационния лист на конкретното устройство за повече информация.

- Всички други комбинации от NVMOP[3:0] не са внедрени.

- Тази функционалност не е налична на всички устройства. Обърнете се към главата „Flash Program Memory“ в спецификационния лист на конкретното устройство за наличните операции.

- Влизането в режим на пестене на енергия след изпълнение на инструкция PWRSAV зависи от завършването на всички чакащи NVM операции.

- Този бит е наличен само на устройства, които поддържат програмиране на редове с RAM буфер. Вижте спецификационния лист с данни за устройството за наличност.

Забележка

- Този бит може да бъде нулиран (т.е. изчистен) само при нулиране при включване (POR).

- При излизане от режим на неактивност има забавяне при включване (TVREG), преди Flash програмната памет да започне да работи. Обърнете се към главата „Електрически характеристики“ на спецификационния лист на конкретното устройство за повече информация.

- Всички други комбинации от NVMOP[3:0] не са внедрени.

- Тази функционалност не е налична на всички устройства. Обърнете се към главата „Flash Program Memory“ в спецификационния лист на конкретното устройство за наличните операции.

- Влизането в режим на пестене на енергия след изпълнение на инструкция PWRSAV зависи от завършването на всички чакащи NVM операции.

- Този бит е наличен само на устройства, които поддържат програмиране на редове с RAM буфер. Вижте спецификационния лист с данни за устройството за наличност.

Регистър 3-2: NVMADRU: горен адресен регистър на енергонезависима памет

Регистър 3-3: NVMADR: Адресен регистър на енергонезависима памет

Регистър 3-4: NVMKEY: Регистър на ключове за енергонезависима памет

САМОПРОГРАМИРАНЕ ПО ВРЕМЕ НА ИЗПЪЛНЕНИЕ (RTSP)

RTSP позволява на потребителското приложение да променя съдържанието на паметта на Flash програмата. RTSP се осъществява с помощта на инструкциите TBLRD (Четене на таблица) и TBLWT (Запис на таблица), регистъра TBLPAG и NVM контролните регистри. С RTSP потребителското приложение може да изтрие една страница от флаш паметта и да програмира две думи с инструкции или до 128 думи с инструкции на определени устройства.

RTSP операция

The dsPIC33/PIC24 Flash program memory array is organized into erase pages that can contain up to 1024 instructions. The double-word programming option is available in all devices in the dsPIC33/PIC24 families. In addition, certain devices have row programming capability, which allows the programming of up to 128 instruction words at a time. Programming and erase operations always occur on an even double programming word, row or page boundaries. Refer to the “Flash Program Memory” chapter of the specific device data sheet for the availability and sizes of a programming row, and the page size for erasing. The Flash program memory implements holding buffers, called write latches, that can contain up to 128 instructions of programming data depending on the device. Prior to the actual programming operation, the write data must be loaded into the write latches. The basic sequence for RTSP is to set up the Table Pointer, TBLPAG register, and then perform a series of TBLWT instructions to load the write latches. Programming is performed by setting the control bits in the NVMCON register. The number of TBLWTL and TBLWTH instructions needed to load the write latches is equal to the number of program words to be written.

Забележка: Препоръчва се регистърът TBLPAG да бъде запазен преди модификация и възстановен след употреба.

ВНИМАНИЕ!

На някои устройства конфигурационните битове се съхраняват в последната страница на потребителското пространство в паметта на Flash програмата в раздел, наречен „Flash Configuration Bytes“. При тези устройства извършването на операция за изтриване на страница на последната страница от паметта на програмата изтрива байтовете за флаш конфигурация, което позволява защита на кода. Следователно потребителите не трябва да извършват операции за изтриване на страницата на последната страница от програмната памет. Това не е проблем, когато битовете за конфигурация се съхраняват в пространството на паметта за конфигурация в раздел, наречен „Регистри за конфигурация на устройството“. Обърнете се към Картата на паметта на програмата в главата „Организация на паметта“ на листа с данни за конкретното устройство, за да определите къде се намират битовете за конфигурация.

Операции за програмиране на Flash

A program or erase operation is necessary for programming or erasing the internal Flash program memory in RTSP mode. The program or erase operation is automatically timed by the device (refer to the specific device data sheet for timing information). Setting the WR bit (NVMCON[15]) starts the operation. The WR bit is automatically cleared when the operation is finished. The CPU stalls until the programming operation is finished. The CPU will not execute any instructions or respond to interrupts during this time. If any interrupts occur during the programming cycle, they will remain pending until the cycle completes. Some dsPIC33/PIC24 devices may provide auxiliary Flash program memory (refer to the “Memory Organization” chapter of the specific device data sheet for details), which allows instruction execution without CPU Stalls while user Flash program memory is being erased and/ or programmed. Conversely, auxiliary Flash program memory can be programmed without CPU Stalls, as long as code is executed from the user Flash program memory. The NVM interrupt can be used to indicate that the programming operation is complete.

Забележка

- Ако възникне събитие POR или BOR, докато се изпълнява операция по изтриване или програмиране на RTSP, операцията RTSP се прекъсва незабавно. Потребителят трябва да изпълни отново RTSP операцията, след като устройството излезе от Нулиране.

- Ако възникне събитие за нулиране на EXTR, SWR, WDTO, TRAPR, CM или IOPUWR, докато се изпълнява операция по изтриване или програмиране на RTSP, устройството ще бъде нулирано само след приключване на операцията по RTSP.

RTSP АЛГОРИТЪМ ЗА ПРОГРАМИРАНЕ

Този раздел описва RTSP програмирането, което се състои от три основни процеса.

Създаване на RAM изображение на страницата с данни, която да бъде модифицирана

Изпълнете тези две стъпки, за да създадете RAM изображение на страницата с данни, която да бъде модифицирана:

- Прочетете страницата на Flash програмната памет и я запазете в RAM за данни като „изображение“ на данни. RAM изображението трябва да се чете, като се започне от границата на адреса на страницата.

- Променете изображението на RAM данните според нуждите.

Erasing Flash Program Memory

След като завършите стъпки 1 и 2 по-горе, изпълнете следните четири стъпки, за да изтриете страницата с флаш програмна памет:

- Задайте битовете NVMOP[3:0] (NVMCON[3:0]), за да изтриете страницата от паметта на Flash програмата, прочетена от Стъпка 1.

- Запишете началния адрес на страницата за изтриване в регистрите NVMADRU и NMVADR.

- С деактивирани прекъсвания:

- a) Запишете последователността от ключове в регистъра NVMKEY, за да активирате настройката на бита WR (NVMCON[15]).

- b) Задайте бита WR; това ще започне цикъла на изтриване.

- c) Изпълнете две NOP инструкции.

- WR битът се изчиства, когато цикълът на изтриване приключи.

Програмиране на страницата с флаш памет

Следващата част от процеса е да програмирате страницата с флаш памет. Страницата с флаш памет се програмира с помощта на данните от изображението, създадено в Стъпка 1. Данните се прехвърлят към ключалките за запис на стъпки или от двойни инструкции или редове. Всички устройства имат възможност за програмиране с двойна инструкция. (Вижте главата „Flash Program Memory“ в информационния лист за конкретното устройство, за да определите дали и какъв тип програмиране на редове е налично.) След зареждане на ключалките за запис се стартира операцията по програмиране, която прехвърля данните от запишете ключалки във флаш памет. Това се повтаря, докато бъде програмирана цялата страница. Повторете следните три стъпки, като започнете от първата дума с инструкции на Flash страницата и увеличавате на стъпки или двойни програмни думи, или редове с инструкции, докато цялата страница бъде програмирана:

- Заредете ключалките за запис:

- a) Настройте регистъра TBLPAG да сочи към местоположението на ключалките за запис.

- b) Заредете желания брой ключалки, като използвате двойки инструкции TBLWTL и TBLWTH:

- За програмиране с две думи са необходими две двойки инструкции TBLWTL и TBLWTH

- За програмиране на редове се изисква двойка инструкции TBLWTL и TBLWTH за всеки елемент от реда на думата с инструкции

- Стартирайте операцията по програмиране:

- a) Задайте битовете NVMOP[3:0] (NVMCON[3:0]), за да програмирате или двойни думи с инструкции, или ред с инструкции, според случая.

b) Запишете първия адрес или на двойната дума с инструкции, или на реда с инструкции, които трябва да бъдат програмирани в регистрите NVMADRU и NVMADR.

c) С деактивирани прекъсвания:

• Запишете последователността от ключове в регистъра NVMKEY, за да активирате настройката на бита WR (NVMCON[15])

• Настройте WR бита; това ще започне цикъла на изтриване

• Изпълнете две NOP инструкции

- a) Задайте битовете NVMOP[3:0] (NVMCON[3:0]), за да програмирате или двойни думи с инструкции, или ред с инструкции, според случая.

- Битът WR се изчиства, когато цикълът на програмиране приключи.

Повторете целия процес, ако е необходимо, за да програмирате желаното количество флаш програмна памет.

Забележка

- Потребителят трябва да помни, че минималното количество памет на Flash програмата, което може да бъде изтрито с помощта на RTSP, е една изтрита страница. Следователно е важно изображение на тези местоположения да бъде съхранено в RAM с общо предназначение, преди да започне цикъл на изтриване.

- Ред или дума във флаш програмната памет не трябва да се програмират повече от два пъти, преди да бъдат изтрити.

- На устройства с конфигурационни байтове, съхранени в последната страница на Flash, извършването на операция за изтриване на страница на последната страница от програмната памет изчиства конфигурационните байтове, което позволява защита на кода. На тези устройства последната страница от флаш паметта не трябва да се изтрива.

ERASING ONE PAGE OF FLASH

Кодовата последователност, показана в Прample 4-1 може да се използва за изтриване на страница от паметта на Flash програма. Регистърът NVMCON е конфигуриран да изтрие една страница от програмната памет. Регистрите NVMADR и NMVADRU се зареждат с началния адрес на страницата, която трябва да бъде изтрита. Паметта на програмата трябва да бъде изтрита на границата на адрес на „четна“ страница. Вижте главата „Flash Program Memory“ в спецификационния лист на конкретното устройство, за да определите размера на Flash страницата.

Операцията по изтриване се инициира чрез записване на специално отключване или последователност от ключове в регистъра NVMKEY преди задаване на бита WR (NVMCON[15]). Последователността за отключване трябва да се изпълни в точния ред, както е показано в Прample 4-1, без прекъсване; следователно прекъсванията трябва да бъдат забранени.

Две NOP инструкции трябва да бъдат вмъкнати в кода след цикъла на изтриване. На някои устройства битовете за конфигурация се съхраняват в последната страница на програмата Flash. При тези устройства извършването на операция за изтриване на страница на последната страница от паметта на програмата изтрива байтовете за флаш конфигурация, което позволява защита на кода като резултат. Потребителите не трябва да извършват операции по изтриване на страница на последната страница от програмната памет.

ЗАРЕЖДАНЕ НА РЕЗАЛИ ЗА ЗАПИС

Ключалките за запис се използват като механизъм за съхранение между записите в таблици на потребителското приложение и действителната последователност на програмиране. По време на операцията по програмиране устройството ще прехвърли данните от ключалките за запис във флаш памет. За устройства, които поддържат програмиране на редове, напрample 4-3 показва последователността от инструкции, които могат да се използват за зареждане на 128 ключалки за запис (128 думи с инструкции). Инструкциите 128 TBLWTL и 128 TBLWTH са необходими за зареждане на ключалките за запис за програмиране на ред от флаш програмна памет. Обърнете се към главата „Flash Program Memory“ в спецификационния лист на конкретното устройство, за да определите броя на ключалки за програмиране, налични на вашето устройство. За устройства, които не поддържат програмиране на редове, напрample 4-4 показва последователността от инструкции, които могат да се използват за зареждане на две резета за запис (две думи с инструкции). Необходими са две TBLWTL и две TBLWTH инструкции за зареждане на ключалките за запис.

Забележка

- Кодът за Load_Write_Latch_Row е показан в Прample 4-3 и кодът за Load_Write_Latch_Word е показан в Прampгл. 4-4. Кодът и в двата примераamples се споменава в следващите exampлес.

- Обърнете се към спецификационния лист на устройството за броя на ключалките.

ПРОГРАМИРАНЕ НА ЕДИН РЕД НАПРAMPLE

Регистърът NVMCON е конфигуриран да програмира един ред от Flash програмна памет. Операцията на програмата се инициира чрез записване на специално отключване или последователност от ключове в регистъра NVMKEY преди задаване на бита WR (NVMCON[15]). Последователността за отключване трябва да се изпълни без прекъсване и в точния ред, както е показано в Прampгл. 4-5. Следователно прекъсванията трябва да бъдат забранени преди запис на последователността.

Забележка: Не всички устройства имат възможност за програмиране на редове. Обърнете се към главата „Flash Program Memory“ в спецификационния лист на конкретното устройство, за да определите дали тази опция е налична.

Две NOP инструкции трябва да бъдат вмъкнати в кода след цикъла на програмиране.

ПРОГРАМИРАНЕ НА РЕДОВЕ С ИЗПОЛЗВАНЕ НА RAM БУФЕР

Избрани устройства dsPIC33 позволяват програмирането на редове да се извършва директно от буферно пространство в RAM за данни, вместо да се преминава през задържащите ключалки за прехвърляне на данни с TBLWT инструкции. Местоположението на RAM буфера се определя от регистъра(ите) NVMSRCADR, който се зарежда с адреса на RAM за данни, съдържащ първата дума от програмни данни, които трябва да бъдат записани.

Преди извършване на програмната операция, буферното пространство в RAM трябва да бъде заредено с реда от данни, които ще бъдат програмирани. RAM паметта може да бъде заредена или в компресиран (опакован), или в некомпресиран формат. Компресираното съхранение използва една дума с данни, за да съхрани най-значимите байтове (MSB) на две съседни програмни думи с данни. Некомпресираният формат използва две думи с данни за всяка програмна дума с данни, като горният байт на всяка друга дума е 00h. Компресираният формат използва около 3/4 от пространството в RAM за данни в сравнение с некомпресирания формат. Некомпресираният формат, от друга страна, имитира структурата на 24-битовата програмна дума с данни, пълна с горния фантомен байт. Форматът на данните се избира от RPDF бита (NVMCON[9]). Тези два формата са показани на фигура 4-1.

След като RAM буферът е зареден, Flash Address Pointers, NVMADR и NVMADRU, се зареждат с 24-битовия начален адрес на Flash реда, който трябва да се запише. Както при програмирането на ключалките за запис, процесът се инициира чрез запис на последователността за отключване на NVM, последвано от настройка на бита WR. Веднъж стартирано, устройството автоматично зарежда правилните ключалки и увеличава NVM адресните регистри, докато всички байтове бъдат програмирани. Прample 4-7 показва примерample на процеса. Ако NVMSRCADR е настроен на такава стойност, че възниква условие за грешка при недостиг на данни, битът URERR (NVMCON[8]) ще бъде настроен да показва условието.

Устройствата, които прилагат програмиране на RAM буферни редове, също така прилагат едно или две ключалки за запис. Те се зареждат с помощта на инструкциите TBLWT и се използват за извършване на операции по програмиране на думи.

ПРОГРАМИРАНЕ НА ДУМИ

Регистърът NVMCON е конфигуриран да програмира две инструкционни думи на Flash програмна памет. Операцията на програмата се инициира чрез записване на специално отключване или последователност от ключове в регистъра NVMKEY преди задаване на бита WR (NVMCON[15]). Последователността за отключване трябва да се изпълни в точния ред, както е показано в Прample 4-8, без прекъсване. Следователно прекъсванията трябва да бъдат забранени преди запис на последователността.

Две NOP инструкции трябва да бъдат вмъкнати в кода след цикъла на програмиране.

Записване в регистрите за конфигурация на устройството

На определени устройства битовете за конфигурация се съхраняват в пространството на конфигурационната памет в раздел, наречен „Регистри за конфигурация на устройството“. На други устройства конфигурационните битове се съхраняват в последната страница на пространството на потребителската памет на програмата Flash в раздел, наречен „Байтове за флаш конфигурация“. При тези устройства извършването на операция за изтриване на страница на последната страница от паметта на програмата изтрива байтовете за флаш конфигурация, което позволява защита на кода. Следователно потребителите не трябва да извършват операции за изтриване на страницата на последната страница от програмната памет. Обърнете се към Картата на паметта на програмата в главата „Организация на паметта“ на листа с данни за конкретното устройство, за да определите къде се намират битовете за конфигурация.

Когато конфигурационните битове се съхраняват в пространството на конфигурационната памет, RTSP може да се използва за запис в конфигурационните регистри на устройството и RTSP позволява всеки конфигурационен регистър да бъде индивидуално презаписан, без първо да се извърши цикъл на изтриване. Трябва да се подхожда с повишено внимание, когато се записват конфигурационните регистри, тъй като те контролират критични работни параметри на устройството, като източник на системен часовник, PLL и WDT активиране.

Процедурата за програмиране на регистър за конфигурация на устройство е подобна на процедурата за програмиране на Flash програмна памет, с изключение на това, че са необходими само TBLWTL инструкции. Това е така, защото горните осем бита във всеки регистър на конфигурацията на устройството не се използват. Освен това, бит 23 от адреса за запис на таблица трябва да бъде настроен за достъп до конфигурационните регистри. Обърнете се към „Конфигурация на устройството“ (DS70000618) в „Справочно ръководство за семейство dsPIC33/PIC24“ и главата „Специални функции“ в спецификационния лист за конкретно устройство за пълно описание на регистрите за конфигурация на устройството.

Забележка

- Записването в регистрите за конфигурация на устройството не е налично във всички устройства. Обърнете се към главата „Специални характеристики“ в спецификационния лист на конкретното устройство, за да определите режимите, които са налични според дефиницията на NVMOP[3:0] битове за конкретното устройство.

- Докато изпълнява RTSP на регистрите за конфигурация на устройството, устройството трябва да работи с помощта на вътрешния FRC осцилатор (без PLL). Ако устройството работи от различен източник на часовник, трябва да се извърши превключване на часовника към вътрешния FRC осцилатор (NOSC[2:0] = 000) преди извършване на RTSP операция в регистрите за конфигурация на устройството.

- Ако битовете за избор на първичен режим на осцилатор (POSCMD[1:0]) в регистъра за конфигурация на осцилатора (FOSC) се препрограмират на нова стойност, потребителят трябва да гарантира, че битовете за режим на превключване на часовника (FCKSM[1:0]) в регистърът FOSC има първоначална програмирана стойност '0', преди извършването на тази RTSP операция.

АЛГОРИТЪМ ЗА ЗАПИС НА КОНФИГУРАЦИОНЕН РЕГИСТЪР

Общата процедура е следната:

- Запишете новата конфигурационна стойност в резето за запис на таблица, като използвате инструкция TBLWTL.

- Конфигурирайте NVMCON за запис в конфигурационен регистър (NVMCON = 0x4000).

- Запишете адреса на регистъра за конфигурация, който да бъде програмиран в регистрите NVMADRU и NVMADR.

- Деактивирайте прекъсванията, ако са разрешени.

- Запишете последователността от ключове в регистъра NVMKEY.

- Стартирайте последователността на запис, като зададете бита WR (NVMCON[15]).

- Разрешете отново прекъсванията, ако е необходимо.

Example 4-10 показва кодовата последователност, която може да се използва за модифициране на регистър за конфигурация на устройство.

РЕГИСТРАЦИЯ КАРТА

Обобщение на регистрите, свързани с Flash програмирането, е предоставено в таблица 5-1.

Този раздел изброява бележки за приложението, които са свързани с този раздел на ръководството. Тези бележки за приложението може да не са написани специално за семействата продукти dsPIC33/PIC24, но концепциите са уместни и могат да се използват с модификация и възможни ограничения. Текущите бележки за приложението, свързани с Flash програмирането, са:

Забележка: Моля, посетете Microchip webсайт (www.microchip.com) за допълнителни бележки за приложението и код напрampфайлове за семействата устройства dsPIC33/PIC24.

ИСТОРИЯ НА РЕВИЗИИТЕ

Ревизия A (август 2009 г.)

Това е първоначалната издадена версия на този документ.

Ревизия B (февруари 2011 г.)

Тази редакция включва следните актуализации:

- Exampлес:

- Премахнато Прample 5-3 и Exampле 5-4

- Актуализирано Прampле 4-1, Прample 4-5 и Exampле 4-10

- Всички препратки към #WR бяха актуализирани до #15 в Exampле 4-1, Прample 4-5 и Exampле 4-8

- Актуализирано е следното в Прampле 4-3:

- Актуализира заглавието „Програмиране с думи“ на „Зареждане на ключалки за запис за програмиране на редове“

- Всяка препратка към #ram_image беше актуализирана до #0xFA

- Добавен епрampле 4-4

- Актуализирано е заглавието в Прampле 4-8

- Бележки:

- Добавени са две бележки в раздел 4.2 „Операции за програмиране на Flash“

- Актуализирана е бележката в раздел 4.5.2 „Зареждане на ключалки за запис“

- Добавени са три бележки в раздел 4.6 „Записване в регистрите за конфигурация на устройството“

- Добавена е бележка 1 в таблица 5-1

- Регистри:

- Актуализирани са стойностите на битовете за NVMOP[3:0]: NVM операция Изберете битове в регистъра за контрол на флаш паметта (NVMCON) (вижте регистър 3-1)

- Раздели:

- Премахнати секции 5.2.1.4 „Режим на писане на думи“ и 5.2.1.5 „Режим на запис на байт“

- Актуализиран раздел 3.0 „Регистри за управление“

- Актуализирано е следното в раздел 4.5.5 „Програмиране с думи“:

- Променено е заглавието на раздела „Програмиране на една дума от флаш памет“ на „Програмиране с думи“

- Актуализиран първия параграф

- Променени са термините „една дума“ на „двойка думи“ във втория параграф

- Добавена е нова стъпка 1 към раздел 4.6.1 „Алгоритъм за запис на регистър на конфигурацията“

- Маси:

- Актуализирана таблица 5-1

- Няколко препратки към програмна памет бяха актуализирани до Flash програмна памет

- Други незначителни актуализации като актуализации на език и форматиране бяха включени в целия документ

Ревизия C (юни 2011 г.)

Тази редакция включва следните актуализации:

- Exampлес:

- Актуализирано Прampле 4-1

- Актуализирано Прampле 4-8

- Бележки:

- Добавена е бележка в раздел 4.1 „Операция на RTSP“

- Добавена е бележка 3 в раздел 4.2 „Операции за програмиране на Flash“

- Добавена е бележка 3 в раздел 4.2.1 „Алгоритъм за програмиране на RTSP“

- Added a note in Section 4.5.1 “Erasing One Page of Flash”

- Добавена е бележка 2 в раздел 4.5.2 „Зареждане на ключове за запис“

- Регистри:

- Актуализира описанието на битовете за битове 15-0 в регистъра на адреса на енергонезависимата памет (вижте регистър 3-3)

- Раздели:

- Актуализиран раздел 4.1 „Операция на RTSP“

- Актуализиран раздел 4.5.5 „Програмиране с думи“

- Други незначителни актуализации като актуализации на език и форматиране бяха включени в целия документ

Ревизия D (декември 2011 г.)

Тази редакция включва следните актуализации:

- Актуализиран раздел 2.1.3 „Резета за запис на таблица“

- Актуализиран раздел 3.2 „Регистър на NVMKEY“

- Актуализирани бележките в NVMCON: Регистър за управление на флаш памет (вижте регистър 3-1)

- Бяха направени обширни актуализации в раздел 4.0 „Самопрограмиране по време на изпълнение (RTSP)“

- Други незначителни актуализации като актуализации на език и форматиране бяха включени в целия документ

Ревизия E (октомври 2018 г.)

Тази редакция включва следните актуализации:

- Добавен епрampле 2-2, Прampле 4-2, Прample 4-6 и Exampле 4-9

- Добавен раздел 4.5.4 „Програмиране на редове с помощта на RAM буфер“

- Актуализиран раздел 1.0 „Въведение“, раздел 3.3 „NVM адресни регистри“, раздел 4.0 „Самопрограмиране по време на изпълнение (RTSP)“ и раздел 4.5.3 „Програмиране на един ред Examp"

- Актуализиран регистър 3-1

- Актуализирано Прampле 4-7

- Актуализирана таблица 5-1

Ревизия F (ноември 2021 г.)

Добавен раздел 3.2.1 „Деактивиране на прекъсвания“.

Актуализирано Прampле 3-1, Прampле 4-1, Прampле 4-2, Прampле 4-5, Прampле 4-6, Прampле 4-7, Прampле 4-8, Прample 4-9 и Exampле 4-10.

Updated Section 3.2 “NVMKEY Register”, Section 4.5.1 “Erasing One Page of Flash”, Section 4.5.3 “Single Row Programming Example” и раздел 4.6.1 „Алгоритъм за запис на конфигурационен регистър”.

Обърнете внимание на следните подробности за функцията за защита на кода на продуктите на Microchip:

- Продуктите на Microchip отговарят на спецификациите, съдържащи се в техния конкретен лист с данни на Microchip.

- Microchip вярва, че семейството му от продукти е безопасно, когато се използва по предвидения начин, в рамките на работните спецификации и при нормални условия.

- Microchip цени и агресивно защитава своите права на интелектуална собственост. Опитите за нарушаване на функциите за защита на кода на продукта на Microchip са строго забранени и могат да нарушат Закона за авторското право в цифровото хилядолетие.

- Нито Microchip, нито друг производител на полупроводници може да гарантира сигурността на своя код. Защитата на кода не означава, че ние гарантираме, че продуктът е „нечуплив“. Защитата на кода непрекъснато се развива. Microchip се ангажира непрекъснато да подобрява функциите за защита на кода на нашите продукти

Тази публикация и информацията тук могат да се използват само с продукти на Microchip, включително за проектиране, тестване и интегриране на продукти на Microchip с вашето приложение. Използването на тази информация по друг начин нарушава тези условия. Информация относно приложенията на устройството се предоставя само за ваше удобство и може да бъде заменена от актуализации. Ваша е отговорността да гарантирате, че вашето приложение отговаря на вашите спецификации. Свържете се с местния търговски офис на Microchip за допълнителна поддръжка или получете допълнителна поддръжка на адрес https://www.microchip.com/en-us/support/design-help/client-supportservices.

ТАЗИ ИНФОРМАЦИЯ СЕ ПРЕДОСТАВЯ ОТ MICROCHIP „КАКТО Е“. MICROCHIP НЕ ПРЕДСТАВЛЯВА НИКАКВИ ПРЕДСТАВЛЕНИЯ ИЛИ ГАРАНЦИИ ОТ КАКЪВТО и да е ВИД, ИЗРИЧНИ ИЛИ КОСВЕНИ СЕ, ПИСМЕНИ ИЛИ УСТНИ, ЗАКОНОВИ ИЛИ ДРУГИ, СВЪРЗАНИ С ИНФОРМАЦИЯТА, ВКЛЮЧИТЕЛНО, НО НЕ САМО КОСВЕНИ ГАРАНЦИИ ЗА НЕНАРУШЕНИЕ, ПРОДАВАЕМОСТ И ГОДНОСТ ESS ЗА ОПРЕДЕЛЕНА ЦЕЛ ИЛИ ГАРАНЦИИ, СВЪРЗАНИ С НЕГОВОТО СЪСТОЯНИЕ, КАЧЕСТВО ИЛИ ИЗПЪЛНЕНИЕ. В НИКАКЪВ СЛУЧАЙ MICROCHIP НЯМА ДА НОСИ ОТГОВОРНОСТ ЗА КАКВАТО И ДА Е НЕПРЯКА, СПЕЦИАЛНА, НАКАЗАТЕЛНА, СЛУЧАЙНА ИЛИ ПОСЛЕДВАЩА ЗАГУБА, ЩЕТА, ЦЕНА ИЛИ РАЗХОД ОТ КАКЪВТО и да е ВИД, СВЪРЗАНИ С ИНФОРМАЦИЯТА ИЛИ НЕЙНОТО ИЗПОЛЗВАНЕ, КАКВОТО И ДА Е ПРИЧИНЕНО, ДОРИ АКО MICROCHIP Е БИЛ EN СЪВЕТВАН С ВЪЗМОЖНОСТТА ИЛИ ЩЕТИТЕ СА ПРЕДВИДИМИ. В НАЙ-ПЪЛНАТА СТЕПЕН, ПОЗВОЛЕНА ОТ ЗАКОНА, ПЪЛНАТА ОТГОВОРНОСТ НА MICROCHIP ПО ВСИЧКИ ИСКОВЕ, СВЪРЗАНИ ПО КАКЪВТО И ДА Е НАЧИН С ИНФОРМАЦИЯТА ИЛИ ИЗПОЛЗВАНЕТО ѝ, НЯМА ДА НАДВИШАВА СУМАТА НА ТАКСИ, АКО ИМА ТАКИВА, КОИТО СТЕ ПЛАТИЛИ ДИРЕКТНО НА MICROCHIP ЗА ИНФОРМАЦИЯТА.

Използването на устройства Microchip в животоподдържащи и/или безопасни приложения е изцяло на риск на купувача и купувачът се съгласява да защитава, обезщетява и предпазва Microchip от всякакви щети, искове, дела или разходи, произтичащи от такава употреба. Никакви лицензи не се предават, имплицитно или по друг начин, съгласно правата на интелектуална собственост на Microchip, освен ако не е посочено друго.

За информация относно системите за управление на качеството на Microchip, моля посетете www.microchip.com/качество.

Търговски марки

Името и логото на Microchip, логото на Microchip, Adaptec, AnyRate, AVR, логото на AVR, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi лого, MOST, MOST лого, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 лого, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST лого, SuperFlash , Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron и XMEGA са регистрирани търговски марки на Microchip Technology Incorporated в САЩ и други страни. AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, лого на ProASIC Plus, Quiet- Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath и ZL са регистрирани търговски марки на Microchip Technology Incorporated в САЩ

Потискане на съседен ключ, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM , ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE , Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-IS, storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect и ZENA са търговски марки на Microchip Technology Incorporated в САЩ и други страни.

SQTP е марка за услуги на Microchip Technology Incorporated в САЩ

Логото на Adaptec, Frequency on Demand, Silicon Storage Technology, Symmcom и Trusted Time са регистрирани търговски марки на Microchip Technology Inc. в други страни.

GestIC е регистрирана търговска марка на Microchip Technology Germany II GmbH & Co. KG, дъщерно дружество на Microchip Technology Inc., в други страни.

Всички останали търговски марки, споменати тук, са собственост на съответните им компании.

© 2009-2021, Microchip Technology Incorporated и нейните филиали.

Всички права запазени.

ISBN: 978-1-5224-9314-3

Световни продажби и обслужване

АМЕРИКИ

- Корпоративен офис

2355 West Chandler Blvd.

Чандлър, AZ 85224-6199

Тел: 480-792-7200

факс: 480-792-7277

Техническа поддръжка: http://www.microchip.com/

подкрепа Web адрес: www.microchip.com - Атланта

Дулут, Джорджия

Тел: 678-957-9614

факс: 678-957-1455 - Остин, Тексас

Тел: 512-257-3370 - Бостън

Уестбъро, Масачузетс

Тел: 774-760-0087

факс: 774-760-0088 - Чикаго

Итаска, Илинойс

Тел: 630-285-0071

факс: 630-285-0075 - Далас

Адисън, Тексас

Тел: 972-818-7423

факс: 972-818-2924 - Детройт

Нови, Мичиган

Тел: 248-848-4000 - Хюстън, Тексас

Тел: 281-894-5983 - Индианаполис

Нобълсвил, IN

Тел: 317-773-8323

факс: 317-773-5453

Тел: 317-536-2380 - Лос Анджелис

Мисия Виехо, Калифорния

Тел: 949-462-9523

факс: 949-462-9608

Тел: 951-273-7800 - Роли, Северна Каролина

Тел: 919-844-7510 - Ню Йорк, Ню Йорк

Тел: 631-435-6000 - Сан Хосе, Калифорния

Тел: 408-735-9110

Тел: 408-436-4270 - Канада – Торонто

Тел: 905-695-1980

факс: 905-695-2078

АЗИЯ/ТИХИЯ ОКЕАН

- Австралия – Сидни

Тел: 61-2-9868-6733 - Китай – Пекин

Тел: 86-10-8569-7000 - Китай – Ченгду

Тел: 86-28-8665-5511 - Китай – Чунцин

Тел: 86-23-8980-9588 - Китай – Дунгуан

Тел: 86-769-8702-9880 - Китай – Гуанджоу

Тел: 86-20-8755-8029 - Китай – Ханджоу

Тел: 86-571-8792-8115 - Китай – САР Хонконг

Тел: 852-2943-5100 - Китай – Нанкин

Тел: 86-25-8473-2460 - Китай – Циндао

Тел: 86-532-8502-7355 - Китай – Шанхай

Тел: 86-21-3326-8000 - Китай – Шенян

Тел: 86-24-2334-2829 - Китай – Шенжен

Тел: 86-755-8864-2200 - Китай – Суджоу

Тел: 86-186-6233-1526 - Китай – Ухан

Тел: 86-27-5980-5300 - Китай – Сиан

Тел: 86-29-8833-7252 - Китай – Ксиамен

Тел: 86-592-2388138 - Китай – Джухай

Тел: 86-756-3210040 - Индия – Бангалор

Тел: 91-80-3090-4444 - Индия – Ню Делхи

Тел: 91-11-4160-8631 - Индия - Пуна

Тел: 91-20-4121-0141 - Япония – Осака

Тел: 81-6-6152-7160 - Япония – Токио

Тел: 81-3-6880-3770 - Корея – Тегу

Тел: 82-53-744-4301 - Корея – Сеул

Тел: 82-2-554-7200 - Малайзия - Куала Лумпур

Тел: 60-3-7651-7906 - Малайзия – Пенанг

Тел: 60-4-227-8870 - Филипини – Манила

Тел: 63-2-634-9065 - Сингапур

Тел: 65-6334-8870 - Тайван – Хсин Чу

Тел: 886-3-577-8366 - Тайван – Гаосюн

Тел: 886-7-213-7830 - Тайван - Тайпе

Тел: 886-2-2508-8600 - Тайланд – Банкок

Тел: 66-2-694-1351 - Виетнам – Хо Ши Мин

Тел: 84-28-5448-2100

ЕВРОПА

- Австрия – Велс

Тел: 43-7242-2244-39

факс: 43-7242-2244-393 - Дания – Копенхаген

Тел: 45-4485-5910

факс: 45-4485-2829 - Финландия – Еспоо

Тел.: 358-9-4520-820 - Франция – Париж

Тел: 33-1-69-53-63-20

факс: 33-1-69-30-90-79 - Германия – Гархинг

Тел: 49-8931-9700 - Германия – Хаан

Тел: 49-2129-3766400 - Германия – Хайлброн

Тел: 49-7131-72400 - Германия – Карлсруе

Тел: 49-721-625370 - Германия – Мюнхен

Тел: 49-89-627-144-0

факс: 49-89-627-144-44 - Германия – Розенхайм

Тел: 49-8031-354-560 - Италия – Милано

Тел: 39-0331-742611

факс: 39-0331-466781 - Италия – Падуа

Тел: 39-049-7625286 - Холандия – Drunen

Тел: 31-416-690399

факс: 31-416-690340 - Норвегия – Трондхайм

Тел: 47-7288-4388 - Полша – Варшава

Тел: 48-22-3325737 - Румъния – Букурещ

Тел: 40-21-407-87-50 - Испания - Мадрид

Тел: 34-91-708-08-90

факс: 34-91-708-08-91 - Швеция – Гьотенберг

Тел: 46-31-704-60-40 - Швеция – Стокхолм

Тел: 46-8-5090-4654 - Великобритания – Уокингам

Тел: 44-118-921-5800

факс: 44-118-921-5820

Забележка:

Този раздел на ръководството за семейни справки е предназначен да служи като допълнение към листовете с данни на устройството. В зависимост от варианта на устройството, този раздел с ръководство може да не се отнася за всички устройства dsPIC33/PIC24. Моля, вижте бележката в началото на главата „Flash Program Memory“ в текущия лист с данни на устройството, за да проверите дали този документ поддържа устройството, което използвате.

Листовете с данни на устройството и секциите на справочното ръководство за семейството са достъпни за изтегляне от Microchip Worldwide Webсайт на: http://www.microchip.com.

Документи / Ресурси

|

MICROCHIP PIC24 Flash програмиране [pdf] Ръководство за потребителя PIC24 Flash програмиране, PIC24, Flash програмиране, програмиране |

|

MICROCHIP PIC24 Flash програмиране [pdf] Ръководство за потребителя PIC24 Flash програмиране, PIC24, Flash програмиране |